The third mode is the one which I've been working on recently and had success with last night. It's one of several proposed 256 colour modes. This one uses the attribute byte to determine the logical ink colour (0-255). The paper colour is determined by the ULA2 border colour stored in a latch at 0x4E3B.

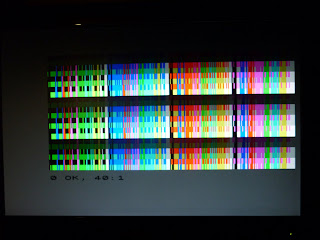

Testing 256 colour mode (mode 72) - random palette

Testing 256 colour mode (mode 72) - random palette

Atic Atac loading in 256 colour mode with a randomised palette.

Note the effects of the timing issue on the Ultimate logo

The rainbow stripes don't work when there's only one paper colour!

(C) 1982 Sinclair Research in lime green.

It had to be done.

There are a number of bugs/"features" with this mode:

- Background colour is dictated by the ULA2 border colour. The ULA2 border is only active when the ULA border is set to black (BORDER 0). Careful manipulation of the ULA2 border colours during the screen refresh should be able to increase the number of colours on-screen. Other, similar effects can be achieved by switching screen mode at appropriate times during screen refresh.

- It follows that setting the ULA border to a colour other than black means you can have a border that doesn't match the 'paper' colour. If the ULA border colour isn't matched in the 256 colour palette, then you have an extra colour on-screen (if anyone's counting).

- A noise effect is notable on the colour whose palette entry is being updated due to lack of contention on the dual-port palette RAM. This could potentially be fixed, however it could also be exploited as a special effect. For now I'm leaving it alone.

- The pixel colour can be selected from BASIC by manipulating ink, paper, bright and flash values.

- As can be seen from the pictures - there are timing issues caused by the palette lookup cycle (at least I think this is the cause). These will need to be fixed, however the display being created is stable, and the which is very encouraging.

Having a single paper colour for the whole screen isn't particularly useful for detailed graphics. Other similar paletted modes are to be implemented which will be more useful:

- 16 inks, 16 papers. Paletted. 2 colours in each 8x8 attribute square

- 32 inks, 8 papers. Paletted. 2 colours in each 8x8 attribute square

- 64 inks, 4 papers. Paletted. 2 colours in each 8x8 attribute square

- 128 inks, 2 papers. Paletted. 2 colours in each 8x8 attribute square

- 256 colours, Paletted. 2 colours in each 8x8 attribute square. 2 byte attributes.

- The above modes, but with 8x1 pixel attributes.

- ULAplus